# Implementation of Adaptive OFDM System Using FPGA

M.A. Mohamed<sup>1</sup>, A.S. Samarah<sup>1</sup>, M.I. Fath Allah<sup>2</sup>

<sup>1</sup> Faculty of Engineering, Mansoura University, Mansoura, Egypt

<sup>2</sup> Delta Higher Institute for Engineering and Technology, Mansoura, Egypt

#### Abstract

OFDM is a modulation as well as multiplexing technique which is now widely used in various high speed mobile and wireless communication systems because of its capacity of ensuring high level robustness against interference. In this paper the design and implementation of OFDM system will be illustrated as well as a detailed simulation of the OFDM system with 64-QAM to study the effect of various design parameters on the system performance. OFDM transceiver will be implemented using FPGA Spartan 3A kit. This adaptive system will be implemented using different digital modulation schemes as shown in the emulation results. All modules are designed using VHDL programming language.

**Keywords:** Orthogonal Frequency Division Multiplexing (OFDM); Field Programmable Gate Array (FPGA); Hardware Description Language (HDL); Inverse Fast Fourier Transform (IFFT); Fast Fourier Transform (FFT); Cyclic Prefix (CP); Bit Error Rate (BER); Signal to Noise Ratio (SNR).

## 1. Introduction

OFDM could be tracked to 1950's but it had become very popular at these days, allowing high speeds at wireless communications [1]. While OFDM has become the core of most 4G communication systems as fixed Wi-Fi system (IEEE802.11a standard), mobile Wi-Fi system (IEEE802.11b standard), fixed WiMAX system (IEEE802.16a standard), mobile WiMAX system (IEEE802.16e standard), and Long Term Evolution (LTE) system; it was essential to build this OFDM system on a suitable hard ware. The aim of our paper is to implement this system to be suitable for all new communication systems. FPGAs are flexible and reconfigurable integrated circuits, whose functionality is programmed by the designer rather than the device manufacturer. Unlike an Application-Specific Integrated Circuit (ASIC), FPGAs can be reprogrammed multiple times, even after deployment. The high speed, parallel architecture provides complete control over the degree of parallelism in the design, and arithmetic word lengths. This flexibility is a key advantage of FPGAs over traditional Digital Signal Processor (DSP) processors. Many recent high speed digital signal processing applications such as networking, video and image

processing and communications are implemented by using FPGA [2]. In our implementation, the emulation time has been made as short as possible. The resources of Xilinx Spartan-3A kit have been suitable for our implementation. This paper aims to give an idea of what is an OFDM system, its implementation and the analysis of the obtained results of the simulations testing. This OFDM system is able to support different M-QAM modulation schemes. The next of this paper is organized as follows; section-III provides the related work, section-III introduces OFDM overview, section-IV presents simulation results, section-V introduces VHDL emulation and conclusions.

## 2. Related Work

Moisés Serra [3] shows the design of an OFDM transmitter as a part of an OFDM demonstrator Hiperlan/2 based, Ma. José Canet [4] shows implementation issues of a digital transmitter for an OFDM based WLAN systems and benchmarks some optimized VHDL area results against System Generator results, Canet's work is focused on the solutions for the OFDM signal generation in base-band and in intermediate frequency (IF). Chris Dick [5] emphasizes the suitability of high-level design tools when designing sophisticated systems, and the importance to design FPGA systems rather than ASIC to one day accomplish the SDR "Software Defined Radio" concept and gives a high-level overview of the FPGA implementation giving some deep to the synchronization, packet detection, preamble correlate channel estimation and equalization; that is mainly at the OFDM receiver. Ludovico de Souza et al. [6] present a FPGA implementation capable to support 802.11 wireless modems but just as a validating and prototyping stage for an ASIC. Joaquin Garcia, Rene Cumplido [7] focuses on the FPGA suitability to support IF processing for the Std. IEEE 802.11a and the resource area and timing requirements either for rapid prototyping or to take advantage of re-configurability in order to be able to support different standards. Y. Awad, L. H. Crockett and R. W. Stewart [8] investigate the efficient FPGA implementation of an OFDM transceiver design for the

IEEE 802.20 physical layer. Paul Guanming Lin [9] demonstrates the concept and feasibility of an OFDM system, and investigates how its performance is changed by varying some of its major parameters. This objective is met by developing a MATLAB program to simulate a basic OFDM system. M. A. Mohamed [10] presents an FPGA technique to gain approach in the problem of OFDM system implementation.

## **3. OFDM Overview**

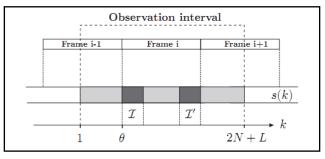

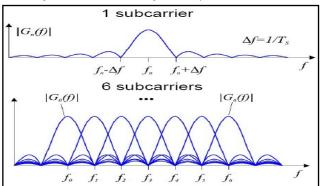

OFDM is an attractive modulation scheme used in broadband wireless systems that encounter large delay spreads. OFDM avoids temporal equalization altogether, using a cyclic prefix technique with a small penalty in channel capacity. Where Line-of-Sight (LoS) cannot be achieved, there is likely to be significant multipath dispersion, which could limit the maximum data rate. Technologies like OFDM are probably best placed to overcome these, allowing nearly arbitrary data rates on dispersive channels. [11]. Each subcarrier can be modulated independently as shown in Fig. 1. The spectra of the subcarriers overlap, but the subcarrier signals are mutually orthogonal as shown in Fig. 2 [11].

Fig.1 Structure of OFDM signal with cyclic extended frames

Fig. 2 OFDM Subcarriers in Frequency Domain

#### 3.1 OFDM Advantages

In general, OFDM systems have the following advantages: (i) efficient use of spectrum.; (ii) resistant to frequency selective fading; (iii) Eliminates ISI (Inter-Symbol Interference) and ICI (Inter-Carrier Interference); (iv) can recover lost symbols due to the frequency selectivity of channels; (v) channel equalization; (vi) computationally efficient [11].

### 3.2 OFDM Disadvantages

OFDM systems have the following disadvantages: (i) High synchronism accuracy; (ii) Multipath propagation must be avoided in other orthogonality not be affected, and (iii) Large peak-to-mean power ratio due to the superposition of all subcarrier signals, this can become a distortion problem (Crest Factor).[11]

#### 3.3 OFDM Transceiver

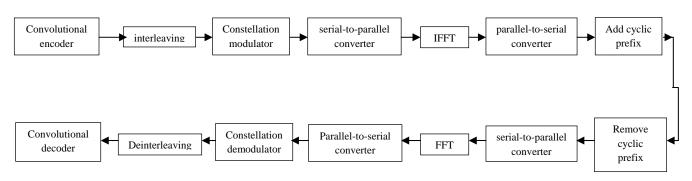

The block diagram of an OFDM transceiver is shown in Fig. 3. [9]. The basic component will be discussed in the next few subsections.

#### 3.3.1 OFDM Transmitter

The main components of OFDM transmitter are shown in Fig.3 [9]. The randomizer is used as random bit generator. The first three blocks are used for data coding and interleaving. The coded bits will be mapped by the constellation modulator using Gray codification, this way an + jbn values are obtained in the constellation of the modulator. The serial to parallel converter converts the data bits from the serial form to the parallel form. The Inverse Fast Fourier Transform (IFFT) transforms the signals from the frequency domain to the time domain; an IFFT converts a number of complex data points, of length that is power of 2, into the same number of points but in the time domain. The number of subcarriers determines how many sub-bands the available spectrum is split into [11, 12]. The Cyclic Prefix (CP) is a copy of the last N samples from the IFFT, which are placed at the beginning of the OFDM frame to overcome ISI problem. It is important to choose the minimum necessary CP to maximize the efficiency of the system [16].

#### 3.3.1 OFDM Receiver

The main blocks of OFDM receiver are observed in Fig.3 [9]. The received signal goes through the cyclic prefix removal and a serial-to-parallel converter [11]. After that, the signals are passed through an N-point fast Fourier transform to convert the signal to frequency domain. The output of the FFT is formed from the first M samples of the output. The demodulation can be made by DFT, or better, by FFT, that is it efficient implementation that can be used reducing the time of processing and the used hardware [14]. FFT calculates DFT with a great reduction in the amount of operations, leaving several existent redundancies in the direct calculation of DFT [13-15].

## 4. Simulation Results

The presented OFDM system in the above few subsections will be simulated using MATLAB-2011 on a personal computer of the following specifications: (i) Intel processor 3.2 GHZ Pentium-four; (ii) 2MB cache RAM; (iii) 2 GB RAM; (iv) SATA hard disk 250GB. In this part the simulation of OFDM system using MATLAB Simulink tools will be obtained. The effect of different parameters on the simulation of the OFDM system using MATLAB program is discussed through the following experiments.

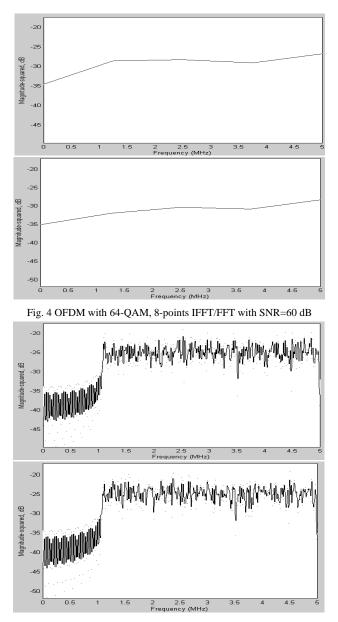

#### 4.1 Experiment-1

In this experiment, the study of changing FFT/IFFT length with fixed SNR will be discussed. The optimum practical value used for the SNR is 60 dB in the case of using Additive White Gaussian Noise (AWGN) channel. The FFT/IFFT lengths that have been used are 8-points, 16points, 32-points, 64-points, 128-points, 256-points, 512 points, and 1024 points. This experiment has been applied on OFDM system with 64-QAM. The simulation results for this experiment are shown in the following figures.

Fig. 5 OFDM with 64-QAM, 1024-points IFFT/FFT with SNR=60 dB

The simulation results for the worst case (8-points FFT) and the best case (1024-points FFT) were presented in the above figures for OFDM with 64-QAM. The result from this experiment is that the more FFT/IFFT length, the more accurate and more practical use of OFDM system; i.e. more subcarriers can be used as shown from the spectra of OFDM signals that are observed in the previouse figures.

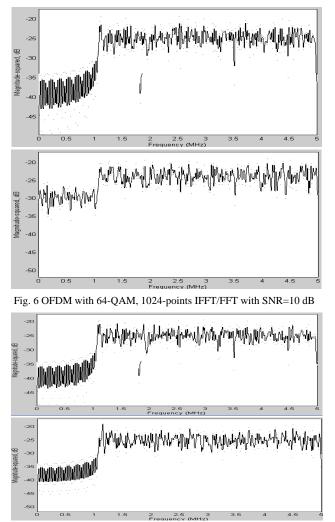

#### 4.2 Experiment-2

In this experiment the study of changing the SNR with fixed FFT/IFFT length will be discussed. The optimum length used for FFT/IFFT is 1024-points as discussed in experiment-1. The SNR values will be from 10dB to 60dB by step of 1dB. This experiment has been applied on OFDM system with 64-QAM. The simulation results for this experiment are shown in the following figures.

Fig. 7 OFDM with 64-QAM, 1024-points IFFT/FFT with SNR=60 dB

Fig. 8 OFDM with 64-QAM, 1024-points IFFT/FFT with SNR=70 dB

The simulation results for the worst case (SNR=10dB) and the best case (SNR=60dB) were presented in the above figures for OFDM with 64-QAM. From the results of this experiment, we get that the optimum value for the SNR is 60dB for minimum AWGN. After this value there is nearly no effect.

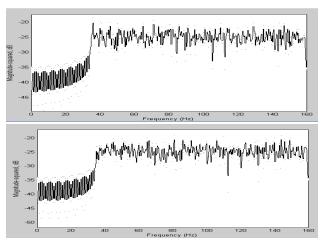

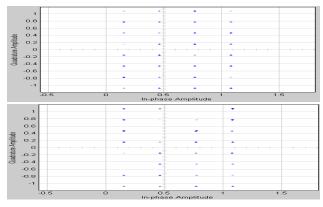

#### 4.3 Experiment-3

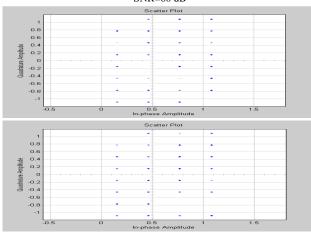

In this experiment we discuss the effect of changing of the SNR over the scatter plot for complex digital modulator/demodulator with the same SNR values as in experiment-2. This experiment has been applied on OFDM system with 64-QAM. The simulation results for this experiment are shown in the following figures.

Fig. 9 OFDM with 64-QAM; scatter plot for modulator/demodulator, SNR=10 dB

IJCSI www.IJCSI.org

Fig. 10 OFDM with 64-QAM; scatter plot for modulator/demodulator, SNR=60 dB

Fig. 11 OFDM with 64-QAM; scatter plot for modulator/demodulator, SNR=70 dB

From the experimental results of this experiment shown in the previous figures we get that the optimum value for the SNR is 60 dB for minimum scattering in the output of the modulator and demodulator.

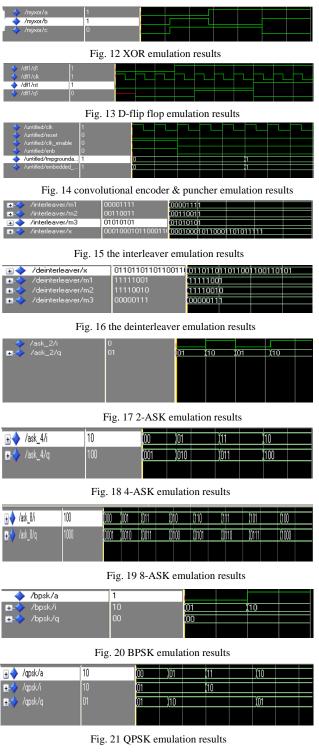

## 5. VHDL Emulation

In this part the emulation of OFDM elements will be implemented. The implementation process will be carried out using the Mentor Graphics tool FPGA-Advantage 7.2 on the same personal computer presented in the simulated part. The first block of the system is the randomizer which consists of two basic parts; the XOR gate and D-flip flop. The second two blocks together are used for data coding. The third block is the interleaver block for further more coding of the input data to be transmitted. The fourth block is the constellation modulator and in our results we will present some different techniques for constellation mapper as; 2-ASK, 4-ASK, 8-ASK, BPSK, QPSK, and 16-PSK so this system is called adaptive system. The next block is the S/P (serial to parallel) converter that is used to convert the data from the serial form to the parallel form to introduce it to IFFT block, and the opposite process in the receiver will be performed using P/S (parallel to serial) converter, the VHDL emulation results for these blocks will be presented in the following figures;

| <b>3∲</b> /qan_16/a 🛛 1111   | <u> </u>         | (010 (Q1                     | 1 (00              | 010 0110                  | 011 (100         | 10        | 101 (1011             | )10              | 1111             | )110 (111 |

|------------------------------|------------------|------------------------------|--------------------|---------------------------|------------------|-----------|-----------------------|------------------|------------------|-----------|

| 🔥 /qan_16/ 🛛 100             | Ű                |                              | (0)                |                           | (01              |           |                       | 10               |                  |           |

| 🐴 /qan_16/q 🛛 100            | <u>00</u> )01    | 01 (11                       | (ii                | )11 (M                    | 10 (11           | )10       | ))1 (10               | M                | 00               | )11 (1)   |

|                              |                  |                              |                    |                           |                  |           |                       |                  |                  |           |

|                              |                  | Fig.                         | 22 16-             | QAM                       | emul             | ation     |                       |                  |                  |           |

| ₽� /s_to_p/di                | 1010101010       | )101010 <mark>1010101</mark> | 010101010101       | 01010101010               | 010              |           |                       |                  |                  |           |

| 🔷 /s_to_p/clk                | 1                |                              |                    |                           |                  |           |                       |                  |                  |           |

| ₽� /s_to_p/do1               | 1010             | 1)0                          | 1                  | <u>(0 (1 (0</u>           | 1)0              | 1 (0 (1.  | (0 )1                 | (0 (1)(          |                  |           |

|                              | 1010             | 1)0                          | 1                  | <u> 10 11 10</u>          | 1)0              | 1 10 11.  |                       | <u>(0 (1 )</u> ( |                  |           |

| <b></b> ↓ /s_to_p/do3        | 1010             | 1                            | 1                  |                           | 1)0              |           |                       | (0)(             |                  |           |

|                              | 1010             | 1)0                          | <u>1,0,1</u>       | <u> 10 11 10</u>          | 1)1              | 1         |                       | 01)              |                  |           |

|                              | 1010             | 1)0                          | 1                  | <u> (0 (1 )0</u>          | 10               | I jQ j.I. |                       | 01)              |                  |           |

|                              | 1010             | <u>1)0</u>                   | <u>]</u>           | <u> 10 11 10</u><br>Vo    | 1)0              | 1         |                       | <u>)0 (1 )(</u>  |                  |           |

|                              | 1010             | l/U                          | 1                  | <u> 10 11 10</u><br>Vo    | 1)0              | 1         |                       | <u>() (1 )(</u>  | ·                |           |

| ₽\$ /s_to_p/do8              | 1010             | <u>()</u>                    | <u>1)())(1</u>     | <u>(0)1)0</u> .           | 1)0              | 1)0)1.    | <u>, U</u> <u>,</u> I | ()(1)(           | <u>) (1 (0</u> . |           |

|                              |                  | Fig. 23                      | the S/             | P emul                    | latior           | n resu    | lts                   |                  |                  |           |

| ₽� /p_to_s/di1               | 0000             | 000                          |                    |                           |                  |           |                       |                  |                  |           |

| <b>⊡{</b> /p_to_s/di2        | 0001             | 001                          |                    |                           |                  |           |                       |                  |                  |           |

| ₽� /p_to_s/d3                | 0010             | 010                          |                    |                           |                  |           |                       |                  |                  |           |

| <mark>⊪</mark> ∲ /p_to_s/di4 | 0011             | 0011                         |                    |                           |                  |           |                       |                  |                  |           |

| <b></b> ↓ /p_to_s/d6         | 0100             | 0100                         |                    |                           |                  |           |                       |                  |                  |           |

| <b></b>                      | 0101             | 0101                         |                    |                           |                  |           |                       |                  |                  |           |

| <b></b> ↓ /p_to_s/di7        |                  | 0110                         |                    |                           |                  |           |                       |                  |                  |           |

| ₽� /p_to_s/dB                |                  | 0111                         |                    |                           |                  |           |                       |                  |                  |           |

| 🔶 /p_to_s/ck                 |                  |                              |                    |                           |                  |           |                       |                  |                  |           |

| ₽� /p_to_s/do                | 0111011001010100 | <u>a. (a. 1a. )a. (a</u> .   | . <u>(0 (0 )</u> 0 | <u>(a., (a., ja., ja.</u> | <u> 0 0.</u> . 0 | (0(0)     | 1 <u>0</u>            | 0)0              | <u>0)0.</u>      | . 0. 0    |

Fig. 24 P/S converter emulation results

The next block is the 8-points IFFT block, and in the receiver the FFT block to reconstruct the carriers. The emulation results for this part will be shown in the following figures;

| /iit/ok       |               | ll      | Л        | תר  | Л    | Л   | Π   | Π  | Л       |     |    |     |  |     |  |     |     |   | ٦    |

|---------------|---------------|---------|----------|-----|------|-----|-----|----|---------|-----|----|-----|--|-----|--|-----|-----|---|------|

| ) /itt/apcade | 111           | 00      | 0        | )01 |      |     |     | Ŭ1 |         |     | 10 |     |  | 101 |  | 110 |     | ľ | ji _ |

| Att/dataa     | 00110011      | 01101   |          |     |      |     |     |    |         |     |    |     |  |     |  |     |     |   |      |

| AtVdatab      |               | 0101010 |          |     |      |     |     |    |         |     |    |     |  |     |  |     |     |   |      |

| Athead        |               | 100100  | (1101111 | )   | W    | UIO | )   | WU |         |     |    | 101 |  |     |  |     | UTO |   |      |

| Ait/tes1      |               |         |          | J   | 0010 |     | 111 |    |         |     |    |     |  |     |  |     |     |   |      |

| Athe2         | 0000011010101 |         |          | ļ   |      |     |     |    | 1101000 | 011 |    |     |  |     |  |     |     |   |      |

Fig. 25 the IFFT emulation results

| 👌 Att/ck      | 1       |        |   |   |     |   |        |     |    |     |   |     |   |      |   |  |

|---------------|---------|--------|---|---|-----|---|--------|-----|----|-----|---|-----|---|------|---|--|

| ₽� /it/apcode |         | 00     | M |   | j)1 |   |        |     | ]1 | 100 |   | 101 |   | (110 |   |  |

| ∎🔶 /lit/dalaa | 0000011 | 00001  |   |   |     |   |        |     |    |     |   |     |   |      |   |  |

| ∎� /it/datab  |         |        |   |   |     |   |        |     |    |     |   |     |   |      |   |  |

| 🔥 /it/eait    | 0000100 | 000010 |   |   | Q   | W |        | 10  |    |     | 0 |     | 1 |      | 1 |  |

| 🔥 /it/eti     |         |        |   | Į |     |   | 100011 | 111 |    |     |   |     |   |      |   |  |

| ₽� /it/tex2   |         |        |   | U |     |   |        |     |    |     |   |     |   |      |   |  |

|               |         |        |   |   |     |   |        |     |    |     |   |     |   |      |   |  |

Fig. 26 the FFT emulation results

The last block in the transmitter is the adding of the cyclic prefix block, the opposite for this block is the first block at the receiver (the removing of the cyclic prefix). The emulation results for these blocks will be illustrated in the following figures;

| /rcp/clk   | 1         |                  |             |            |      |

|------------|-----------|------------------|-------------|------------|------|

| 🔶 /rcp/rst | 0         |                  |             |            |      |

| 🔶 /rcp/en  | 1         |                  |             |            |      |

|            | 111100001 | 11110000         | 111         |            |      |

|            | 11110000  | <u>,11110000</u> | sim:/r<br>1 | rp/en 8 86 | 0 ns |

Fig. 28 removing cyclic prefix emulation results

## 6. Conclusions

The performance of OFDM system with 64-QAM has been simulated using MATLAB toolboxes. There were three experiments for that; (i) the first experiment sudied the changing of FFT/IFFT length with fixed SNR, (ii) the second experiment discussed the changing of the SNR with fixed FFT/IFFT length, and (iii) the third experiment presented the effect of the variation of the SNR over the scatter plot at the demodulator. The main results of these experiments were that the optimum FFT/IFFT length was 1024 points and the best value for the SNR was 60dB; and we get that after this value there is no effect of varying the SNR value. After that the VHDL emulation of OFDM system with different digital modulation schemes has been observed, then we could implement this system on Xillinx Spartan 3-A kit.

#### References

- [1] S. J. Vaughan-Nichols, "OFDM: Back to the Wireless Future," IEEE Computer, pp. 19–21, vol.35, issue 12, Dec. 2002.

- [2] Steepest Ascent Ltd., The DSPedia (www.steepestascent. com), last access Nov. 2011.

- [3] M. Serra, J. Ordiex, P. Marti and J. Carrabina, "OFDM Demonstrator: Transmitter" in Proc 7th International OFDM Workshop 2002, Sep 200.

- [4] Ma. J. Canet, F. Vicedo, J. Valls and V. Almenar, "Design of a Digital Front-End Transmitter For OFDM-WLAN Systems Using FPGA", Control, Communications and Signal Processing 2004, First International Symposium on, pp: 503– 506, 2004.

- [5] C. Dick and F. Harris, "FPGA Implementation of an OFDM PHY" Signals, Systems and Computers, 2003. Conference Record of the Thirty-Seventh Asilomar Conference, Vol.1, pp: 905–909, Nov. 2003.

- [6] L. de Souza, P. Ryan, J. Crawford, K. Wong, G. Zyner and T. McDermott, "Rapid Prototyping of 802.11 wireless modems", Solid-State Circuits Conference, 2001. Digest of Technical Papers. ISSCC 2001 IEEE International, pp: 339-495, Feb.2001

- [7] Y. Kim, H. Jung, H. Ho Lee and K. Rok Cho and F. Harris, "MAC Implementation for IEEE 802.11 Wireless LAN", ATM (ICATM 2001) and High Speed Intelligent Internet Symposium, 2001. Joint 4th IEEE International Conference on, pp. 192–195, Apr. 2001.

- [8] Y. Awad, L. H. Crockett and R. W. Stewart, "OFDM TRANSCEIVER FOR IEEE 802.20 STANDARDS".

- [9] P. G. Lin, "OFDM simulation in MATLAB", a senior project, faculty of California Polytechnic State University, San Luis Obispo, June 2010.

- [10] M. A. Mohamed, "FPGA-BASED DESIGN OF OFDM SYSTEM", the Mediterranean Journal of Computers and Networks, Vol. 7, No. 1, pp: 163-170, 2011.

- [11] F. M. Gutierrez, P. L. Gilabert, "Implementation of a Tx/Rx OFDM system in a FPGA," Master thesis, Francisco Martin Gutierrez, April, 30th 2009.

- [12] K. A. Kadiran, "Design and implementation of OFDM transmitter and receiver on FPGA hardware", Master thesis, Universiti Teknologi Malaysia, 10 November 2005.

- [13] A. Cortés, I. Vélez, I. Zalbide, A. Irizar, and J. F. Sevillano, "An FFT Core for DVB-T/DVB-H Receivers," VLSI Design, vol. 2008, Article ID 610420, 9-pages, 2008.

- [14] Z. Sun, X. Liu, and Z. Ji, "The Design of Radix-4 FFT by FPGA," International Symposium on Intelligent Information Technology Application Workshops, 2008, pp.765-768.

- [15] Datasheet. September 2008, "Xilinx LogiCore Fast Fourier Transform," Version 4.1, Xilinx Inc. Available: http://www.xilinx.com.

- [16] M. Helaoui, S. Boumaiza, A. Ghazel, and F. M. Ghannouchi, "On the RF/DSP design for efficiency of OFDM transmitters," IEEE Trans. Microw. Theory and Tech., vol. 53, no. 7, pp. 2355-2361, Jul. 2005.

- [17] N. Balaji, K. Subba Rao, and M. Srinivasa Rao. 2009. " FPGA Implementation of Ternary Pulse Compression Sequences with Superior Merit Factors," NAUN international Journal of Circuits, systems and signal processing. Volume 2, issue 3, pp. 47-54. Available: http://www.naun.org/journals/circuitssystemssignal/

- [18] User Guide. January 2009, "Virtex-5 FPGA XtremeDSP Design Considerations," Version3.3, Xilinx Inc. Available: http://www.xilinx.com.

- [19] P. L. Gilabert, A. Cesari, G. Montoro, E. Bertran and J. M. Dilhac "Multi Look-Up Table FPGA Implementation of an Adaptive Digital Predistorter for Linearizing RF Power Amplifiers with Memory Effects," IEEE Trans. Microw. Theory and Tech., vol. 56, n? 2, pp. 372 - 384, Feb. 2008

- [20]F.B.O. Bartzoudis, N. Pascual-Iserte, A. L'opezBueno, "Design/ Implementation and Testing of a Real Time Mobile WiMA X Testbed Featuring MIMO Technology. In: 6th International ICST Conference Testbed and Research Infrastructures Development of Networks and Communications (Trident Com), Berlin 2010.

[21] Lecture Notes of the Institute for Computer Sciences, Social-Informatics and Telecommunications Engineering (LNICST), Vol. 46, num.5, PP.199-208 (2011).

**Mohamed Abdel-Azim** received the PhD degree in Electronics and Communications Engineering from the Faculty of Engineering-Mansoura University-Egypt by 2006. After that he worked as an assistant professor at the Electronics & Communications engineering department until now. He has 44publications in various international journals and conferences. His current research interests are in multimedia processing, wireless communication systems, and FPGA applications.

**Mohamed Ismail** received the BSC degree in Electronics and Communications Engineering from the Faculty of Engineering-Mansoura University-Egypt by 2007. After that he worked as a demonstrator at the Electronics & Communications department, Delta Higher Institute For Engineering & Technology. His current research interests are in wireless communication systems and FPGA applications.